主要功能

- 完全整合1553A/B Notice 2, McAir, STANAG 3838接口终端

- 兼容ACE与Mini-ACE系列

- 配置选项:

- RT 或 BC/RT/MT 内建4Kx16内存

- BC/RT/MT内建64Kx17内存支持奇偶校验

- 逻辑接口可选5V或3.3V,+5V收发器,兼容1760或兼容McAir可选

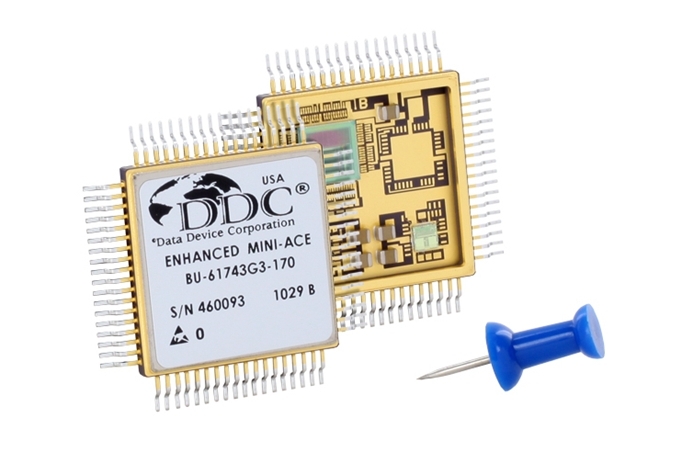

- 1”陶瓷封装Flatpack或Gull Wing

- 内建丰富自测试程序

- 灵活的处理器/储存界面,减少主机等待时间

- 可选10, 12, 16, or 20 MHz时钟频率

- 高度自动化BC架构,内建消息序列控制:

- 消息帧排程

- 消息分流

- 异步消息插入

- 通用功能序列GPQ

- 用户定义终端

- 先进的RT功能:

- 全局循坏缓冲

- 中断状态队列

- 50% 循环缓冲返回中断

- 选择性消息监控

- 基于RT地址,T/R位,子地址进行消息选取

- 命令和数据堆栈

- 50%和100%堆栈返回中断

- 完整军用级Mil-Prf-38534筛选和全军温

PCI 版本:

- 32-bit/33 MHz, 3.3 Volt PCI Target 接口

应用范畴

用于航空电子、地面车辆和其他军事航空航天应用的可靠成熟的COTS现成胶辊解决方案,Enhanced MiniACE系列与DDC早期的ACE系列Mil-Std-1553终端兼容。

Enhanced MiniACE系列提供了主机处理器和1553总线之间的完整接口,集成了双收发器、协议逻辑和4k或64k字的内存。 终端提供5V或3.3V逻辑电平的选择,并具有Mil-Std-1553a/b和STANAG3838的多种协议支持,包括包含McAir兼容收发器的版本。 有10,12,16或20MHz时钟的选择。具有64k个字内存的BC/RT/MT版本内存内建实时奇偶校验。

BC特性包括一个内置的可编程消息序列控制引擎,它有一组20条指令.. 该功能提供了实现多帧消息调度、消息重试方案、数据双缓冲、异步消息插入和向主机CPU报告的自主操作。

RT模式提供了与ACE和MiniACE相同的子地址缓冲机制,以及全局循环缓冲选项、循环缓冲区的50%翻转中断、中断状态队列和支持Mil-Std-1760的“自动启动”选项。

Enhanced MiniACE内建一个全自动的自测试引擎,提供内部协议逻辑和/或RAM的全面测试。

终端在主机接口配置上提供了与ACE和MiniACE相同的灵活性,同时减少了主机处理器在极端情况下的延迟时间。大多数软件功能与前代的ACE和MiniACE系列兼容。

Enhanced MiniACE架构后续的MiniACE Mark3系列和MicroACE TE系列,提供了几种新的封装,电源电压和后端接口。

PCI接口版本的Enhanced MiniACE Mil-Std-1553系列是一种完全集成的解决方案,用于连接32位/33MHz的PCI总线和Mil-Std-1553总线。 与多个独立元器件的设计相比,PCI Enhanced MiniACE减少了板卡空间和供电需求,同时通过向嵌入式PCI总线提供直接接口来消除对自定义FPGA逻辑的需求。 为了加速主机写入操作,该接口包含一个内置的FIFO,使PCI Master主服务器能够在大约1.5µs内传输32字的1553消息。